Last Updated: April 4, 2014

Accellera’s recently released UVM may change the future of verification, as verification methodology seems to be consolidated in this UVM. This post will provide a simple tutorial on this new verification methodology. Rather than focusing on AXI, OCP, or other system buses in existence, this tutorial will be based on the hypothetical example of a jelly-bean generator. The test bench will generate many jelly-bean flavors in a constrained random manner and the system will evaluate palatable flavors. This does not require the knowledge of any system bus.

Accellera’s recently released UVM may change the future of verification, as verification methodology seems to be consolidated in this UVM. This post will provide a simple tutorial on this new verification methodology. Rather than focusing on AXI, OCP, or other system buses in existence, this tutorial will be based on the hypothetical example of a jelly-bean generator. The test bench will generate many jelly-bean flavors in a constrained random manner and the system will evaluate palatable flavors. This does not require the knowledge of any system bus.

The verification components used in the process will be described below.

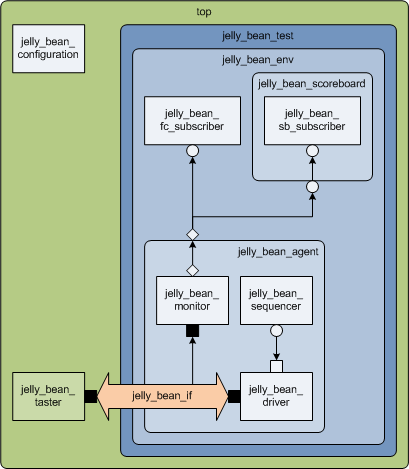

The left figure shows the relationship of the verification components. The jelly_bean_taster is the design-under-test (DUT) module.

The jelly_bean_sequencer will create jelly-bean recipes and send them to the jelly_bean_driver. From the information provided in the recipe, the driver creates jelly beans. The driver passes the jelly beans through the jelly-bean interface (jelly_bean_if) to the jelly_bean_taster, which will check the jelly-bean taste.

Concurrently, as the jelly beans are being created, the jelly_bean_monitor will capture the flavor and color of the recently produced. This information will be passed down to the jelly-bean functional coverage subscriber, referred to as the jelly_bean_fc_subscriber. The subscriber records and totals the jelly beans based on their color and flavor.

The jelly_bean_scoreboard is a component that checks if the jelly_bean_taster is responding correctly. The scoreboard subscribes the information from the jelly_bean_monitor.

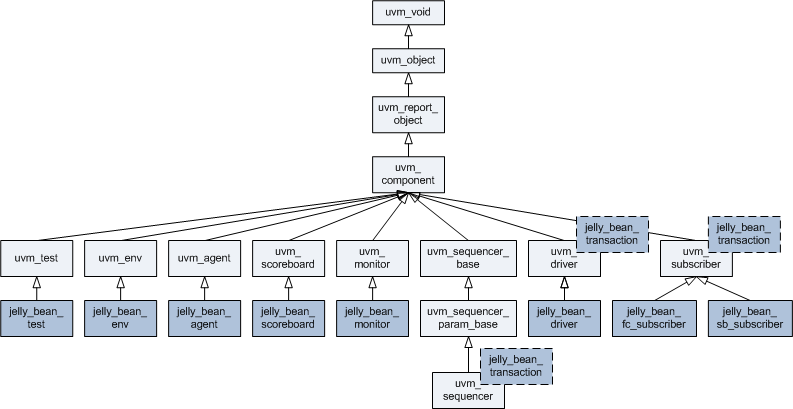

The second figure shows the verification components in a class diagram. The light blue boxes refer to the classes in the UVM basic class library, while the darker boxes indicate the classes created in this tutorial.

Though the post ends here, the next will show the structure of the jelly-bean recipes.

I use Synopsys vcs to run jb1.sv, get this error at simulation

then I run jb2.sv, and got this error

what is wrong in both cases???

Hello,

For the

jb1.svto work, you must use+UVM_TESTNAME=jelly_bean_testoption when you run VCS.I had a bug in

jb2.sv. I forgot to code thenew()function of thejelly_bean_recipe_virtual_sequenceclass. I have already fixed the bug, and the new code is ready to download. Thank you for pointing out the bug.Hi Keisuke,

I am set to verify a RTL model based on C-Golden Ref.Model. Here I would like to write into the UVM registers all the required configurations and pass the same to C & RTL. And I am familiar with UVM registers configurations and DPI calls from SV to C.

But, I am not sure how to implement the DPI’s in UVM.

1) How/where do we add DPI calls and C-functions in the test so that the C-Code runs at first and then dumps the values to some dynamic arrays and later, I access them to compare the results with RTL in the scoreoard ?

Can you please add some example to this. It would be some immense help

Thank You in Advance..!

Surya

Hi Surya,

I am not sure if I understand your question correctly, but you can call your C-functions from the

main_phaseof your test to generate expected values. As you mentioned, you can store the expected values in a dynamic array and use them later in the scoreboard. Did I answer your question?Hi Keisuke,

Appreciate your work done on this site – makes UVM world more clear and easy to understand.

Just one question: do you have this UVM tutorial (each lesson) in other formats (presentations – ppt, with sound and everything)?

Maybe somewhere on youtube? It will be interesting to have access to each lesson in a presentation format to listen as a class …

Thank you.

Adi

That’s a good idea, but unfortunately I don’t have a presentation for the tutorial. I’ll put this on my (long) to-do list. Thanks.

Thank you for this tutorial, Keisuke.

I assume, the makefile was written for Linux. I use questasim and run it on Windows 7. Can you tell me, how should i modify this makefile and what do i have to do to execute it?

Thanks.

Borya

Unfortunately, I have no access to the Window-version of QuestaSim. You can still run a simulation on EDA Playground, though.

Dear Borya,

What version of questasim you are running ? I think I can help you a lot.

Tuyen, it’s Questasim 10.0b. I ‘ve tried to write a do-file with a following code:

vsim work.top +UVM_TESTNAME = jelly_bean_test

seems like it works fine, but i still don’t know how to adopt lines

and so on.

I’ll be very grateful, if you tell me, how to do it

Dear Borya,

What operating system do you run questasim.

If you run in linux you just run follow command:”make questa TUTORIAL=6″

I had try it, it work well. If you have any concern, please let me know.

Thanks alot !!! it worked me too

Hi Keisuke Shimizu,

Appreciate your work with this blog.

I observed in your source on using “uvm_resource_db”.

But, we use “uvm_config_db”. Can you please elaborate

the pros and cons of both. And, the recommended one.

= Murugesan

A general rule of thumb is that you should use

uvm_config_dbif a hierarchical context is important, otherwiseuvm_resource_dbshould be used. For example, thesetfunction ofuvm_config_dbtakes auvm_componentas the first argument to facilitate the specification of the hierarchical context.whereas the

setfunction ofuvm_resource_dbdoesn’t:Having said that, we used

uvm_resource_dbin our tutorial. We should have useduvm_config_dbinstead.Keisuke,

I struggle a long time about the UVM compilation. Would you please share me some clue about debug the errors as follows? I had add the

I think we do not need to do typedef for clk_trans, right?

Thanks,

clk_trans trans = clk_trans::type_id::create("trans"); | ncvlog: *E,SVNOTY (/export/home/basin/kevin.chen/prj/ov9281_uvm/frontend/uvm/tb/agent/clk_agent/clk_seq_lib.sv,27|16): Syntactically this identifier appears to begin a datatype but it does not refer to a visible datatype in the current scope.Here is the lines I try to do the setting of UVM, I also add import uvm_pkg::*; and include “uvm_macros.svh” at the top of all the files.

Do you compile the file that defines the

clk_transclass?Hi Keisuke,

Yes, i got the root cause of it. There is a typo for the ifdef. Would you please tell me is there any reason why we use this piece of code?

Thank you very much

Best

It is called include guard, which avoids compiling the same definition more than once.

But what is the cntxt specified here

Typically

thisis used as the context. Please see this article for more detail.Hi Keisuke,

I am getting the following error when running on vcs.. please help me to resolve this

make[1]: *** [product_timestamp] Error 1

make[1]: Leaving directory `uvm-tutorial-for-candy-lovers-master/run/csrc’

Make exited with status 2

I’m afraid that I don’t know the root cause of the problem. Look at the messages before these lines. That might help.

Hello Keisuke,

Thanks for your efforts .

This is the best blog I came across on UVM.

All the best ..keep rocking .